Przekształtnik AC/AC wysokiej częstotliwości 100kHz część 4

Sterownik bramkowy (ang. Gate driver)

Aby poprawnie wysterować bramkę tranzystora MOSFET należy zadbać o to, aby przełączenie ze stanu niskiego w stan wysoki oraz ze stanu wysokiego w stan niski trwało odpowiednio krótko. Napięcie G-S tranzystora musi

być wystarczające do pełnego wysterowania tranzystora. W przypadku kiedy napięcie bramki będzie niewystarczające do pełnego otwarcia tranzystora sterownik tranzystorów MOSFET nie powinien podać sygnału bramkowego, gdyż w przeciwnym wypadku uszkodzeniu mógłby ulec podzespół półprzewodnikowy.

Podczas pracy tranzystora przy niepełnym napięciu bramki, kiedy płynie przez niego prąd to wydziela się na nim znaczna moc, większa od tej, którą jest w stanie odprowadzić do otoczenia.

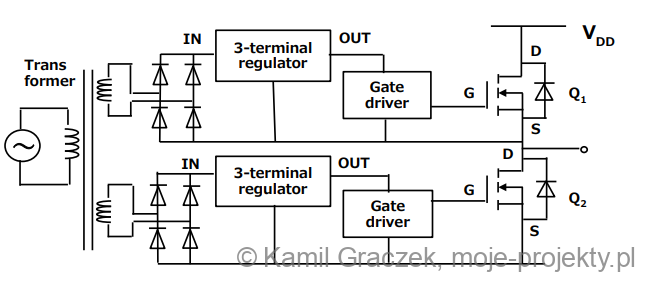

Na rys. 1[1] przedstawiono ideę sterowania pół-mostka H pochodzącą z opracowania Toshiby na temat układów bramkowych tranzystorów MOSFET.

[1] Toshiba. MOSFET Gate Drive Circuit. 26 07 2018. <https://toshiba.semicon-storage.com/info/docget.jsp?did=59460>.

Pomiary oscyloskopowe sterownika bramek tranzystorów

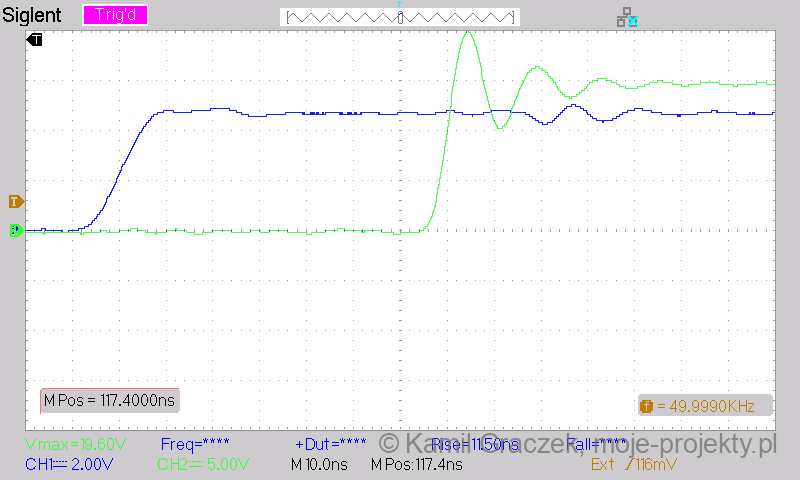

Na rys. 2 przedstawiono zachowanie się sterownika bramkowego przy częstotliwości f=100kHz. Napięcie wejściowe 7,5 Vpp, napięcie na wyjściu 15,60 Vpp. Pomiar wykonano podając przebieg PWM z generatora arbitralnego na wejście sygnałowe sterownika tranzystorów MOSFET.

Rys. 3 Czas narastania przebiegu przy f=100kHz, 11,5ns

Na rys. 3 przedstawiono moment zmiany stanu wyjścia sterownika tranzystorów MOSFET po podaniu stanu wysokiego na wejście (kolor nieb.). Dla obserwowanego przebiegu zmierzono czas narastania tR =11,5 ns, oraz opóźnienie miedzy pojawieniem się stanu wysokiego na wejściu, a załączeniem wyjścia sterownika wynoszące tD=60 ns.